VIAMP

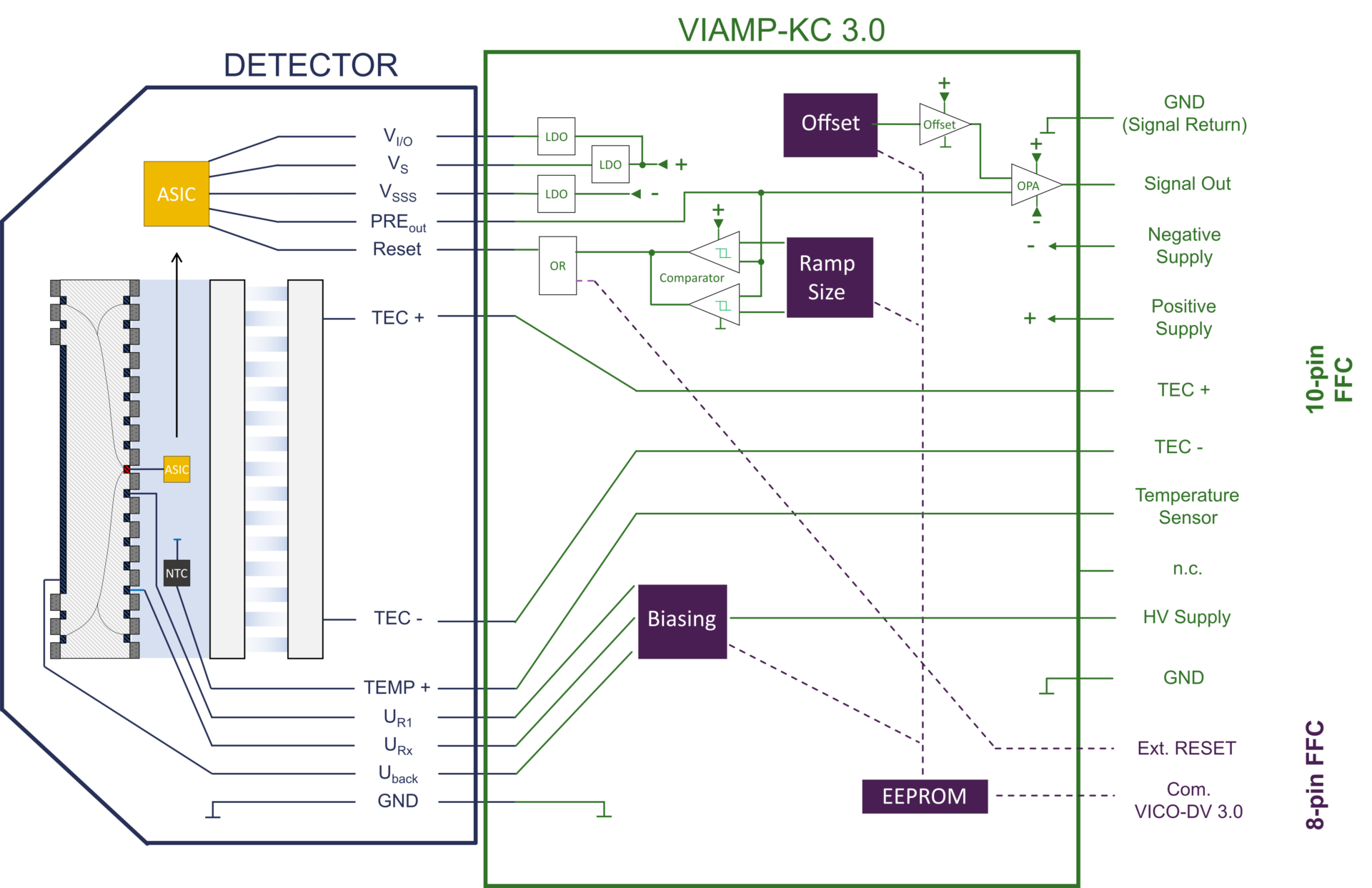

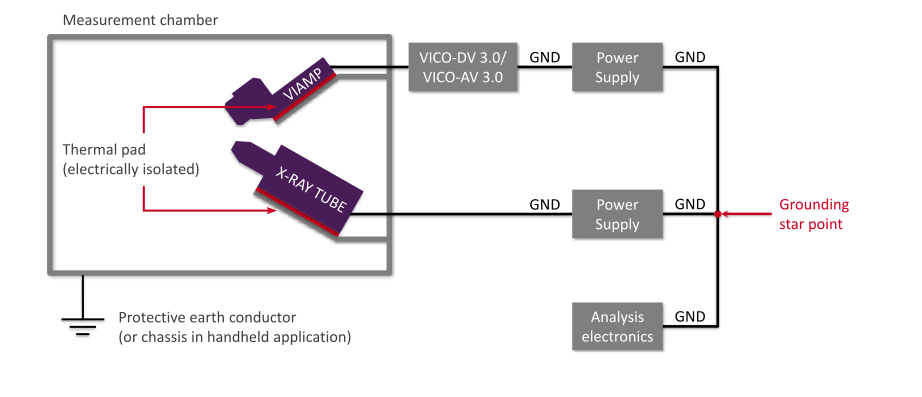

The VIAMP preamplifier modules are specially designed printed circuit boards for operation with KETEK’s VITUS Silicon Drift Detectors (SDD). The assembly comprises an ultra-low noise, ramped reset type electronic preamplifier of positive polarity with onboard settings and filtering for all necessary SDD bias voltages.

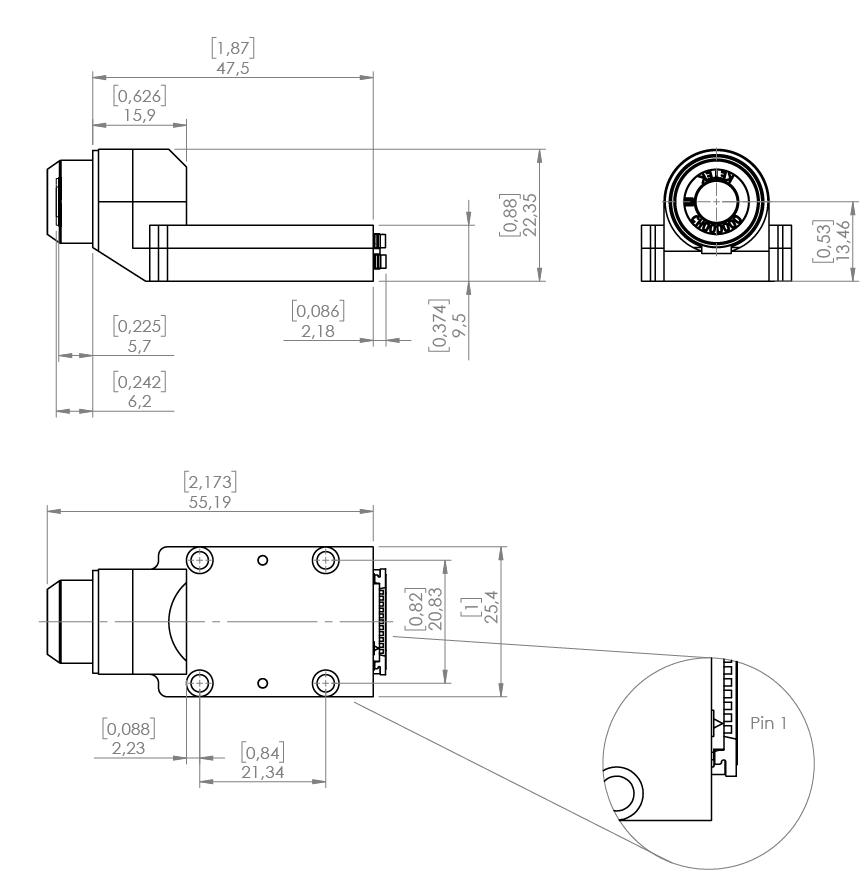

Depending on the size and application of the SDD module, three standard Aluminum housing options are available for the electronic boards, which provide appropriate protection and serve as a sufficient heat sink.

VIAMP-KC 3.0

VIAMP-KC 3.0 with standard housing for VITUS modules H7 to H50

Unique Features

- Ultra-low noise preamplifier

- Ramped output, positive polarity

- Low power consumption

- Available with Graphene based VITUS SDDs

- Improved quantum efficiency for higher energies in combination with VICO-DV 3.0 with KETEK DPP3

- Flex lead connection lengths from 50 mm to 200 mm

- OEM solution for mobile XRF applications

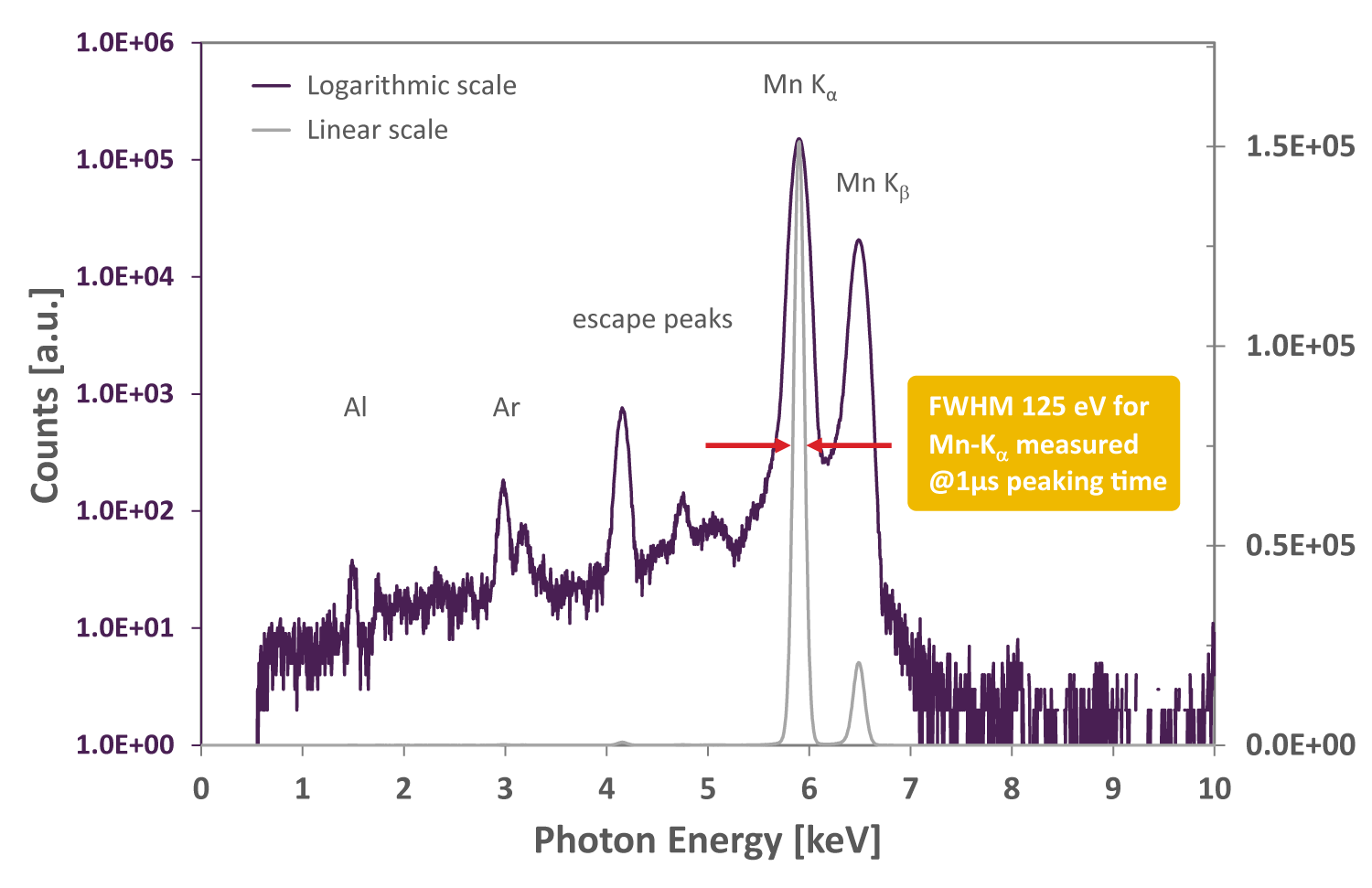

- Guaranteed energy resolution for Mn-Kα-line: FWHM < 133eV @

1 μs peaking time and −35 °C SDD chip temperature - Guaranteed peak to background > 15,000, typical > 20,000

- Other housing designs on request

Specifications

| First amplification stage | KETEK CSA |

| Energy resolution (@ Mn-Kα, -35 °C chip temperature and 1 µs peaking time) | ≤ 133 eV |

| Peak to background | > 15,000 |

| Peak to tail | > 2,000 |

| Peak shift stability up to 100 kcps | < 1 eV |

| Max. input countrate | 2,000 kcps |

| Graphene CH window

Graphene CL window |

1 μm Carbon

165 nm Carbon |

| Cooling performance at +20 °C heat sink temperature |

∆T > 85 K |

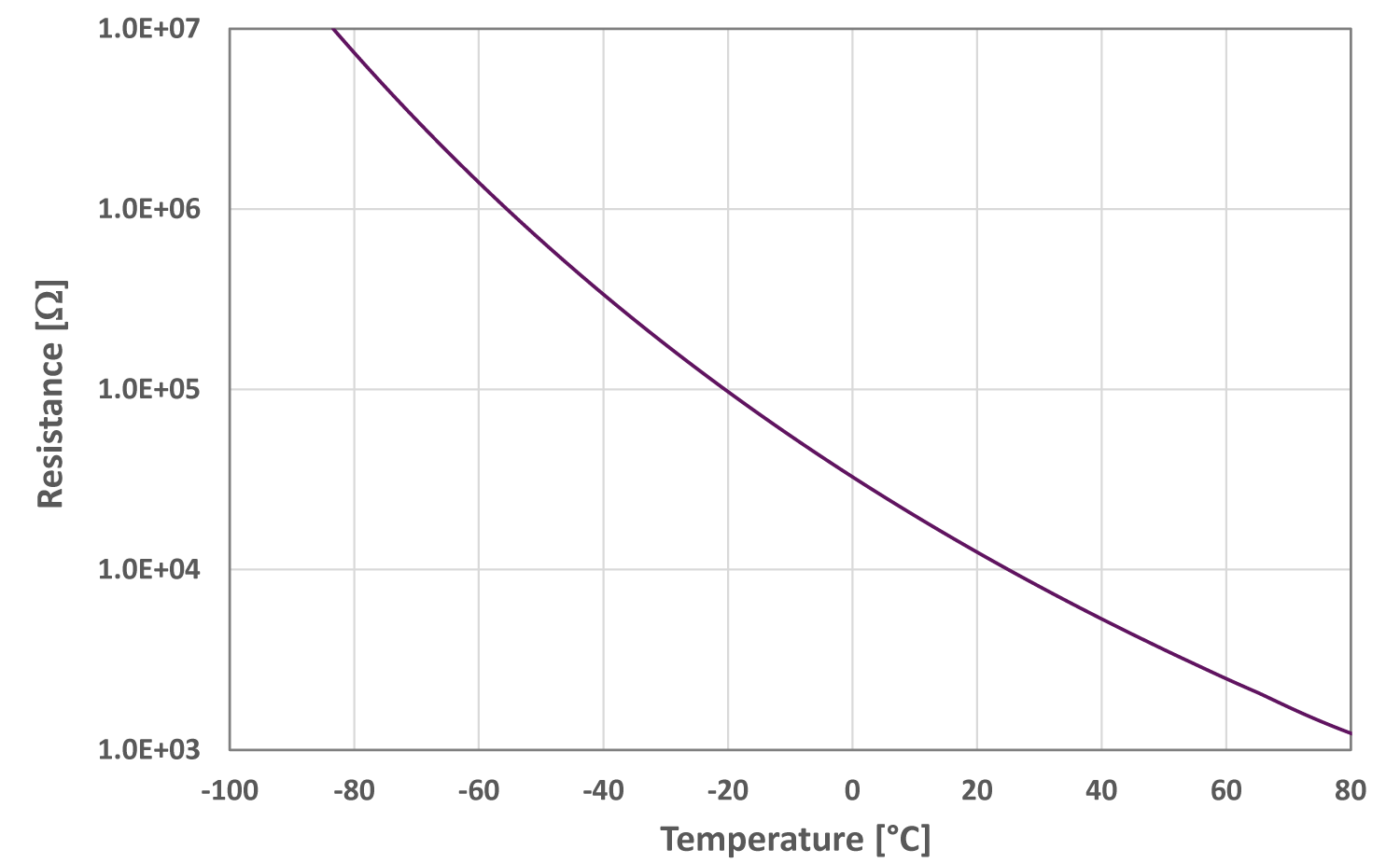

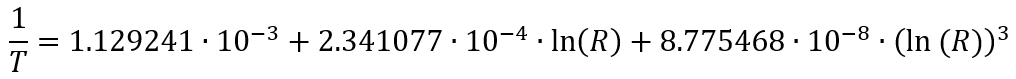

Spectrum

Energy Resolution

Operating Parameters

| Parameter | Typical | Maximum Ratings |

| Positive Power Supply DC | +5 V 18 mA |

+4.9 V to +5.4 V 22 mA max |

| Negative Power Supply DC | -5 V 8 mA |

-5.4 V to -4.9 V 12 mA max |

| Output Signal | Positive Ramp | |

| Output Amplitude | ±0.975 V | ±0.95 Vpp,min ±1.0 Vpp,max |

| Output Gain* | 5 mV/keV | ±20 % |

| Gain Stability | < 20 ppm/°C | |

| External Reset (VICO-DV 3.0) | 0 V or + 3.3 V | |

| HV Supply DC | -168 V ≈ 95 µA |

±5 V 110 µA max |

| TEC Supply DC | 157 mA / 1.58 V @ -35 °C | 500 mA / 7 V |

| TEC ∆T | > 85 K @ +20 °C heat sink temp. | |

| Temp. Sensor | 10 kΩ Thermistor @ +25 °C | ≤ 1 µA |

| * other gain on request |

FFC connection

Pin Assignment 10-Pin FFC

| Pin 1 | TEC Return |

| Pin 2 | TEC Supply |

| Pin 3 | Positive Supply |

| Pin 4 | Negative Supply |

| Pin 5 | GND (Signal Return) |

| Pin 6 | Signal Out |

| Pin 7 | Temperature Sensor |

| Pin 8 | GND |

| Pin 9 | Not Connected |

| Pin 10 | HV Supply |